http://joape.uma.ac.ir

# Analysis and Design of a New Single Switch Non-Isolated Buck-Boost DC-DC Converter

M. R. Banaei<sup>\*</sup>, H. Ajdar Faeghi Bonab, N. Taghizadegan Kalantari

Department of Electrical Engineering, Azarbaijan Shahid Madani University, Tabriz, Iran Research Institute of Applied Power System Studies, Azarbaijan Shahid Madani University, Tabriz, Iran

Abstract- In this paper, a new transformerless buck-boost converter based on ZETA converter is introduced. The proposed converter has the ZETA converter advantages such as, buck-boost capability and input to output DC insulation. The suggested converter voltage gain is higher than the classic ZETA converter. In the presented converter, only one main switch is utilized. The proposed converter offers low voltage stress of the switch; therefore, the low on-state resistance of the main switch can be selected to decrease losses of the switch. The presented converter topology is simple; hence, the control of the converter is simple. The mathematical analyses of the proposed converter are given. The experimental results confirm the correctness of the analysis.

Keyword: Transformerless buck-boost converter, voltage gain, main switch, voltage stress.

# 1. INTRODUCTION

Fossil fuels are vital sources and these fuels are utilized widely in recent years. Fossil fuels have produced many problems such as air pollution, climate change, global warming problems, and other similar troubles to the environment. Renewable energy systems have been distinguished as the best alternative to fossil fuels [1-3]. Fuel cell and Photovoltaic (PV) are the two main renewable energy sources. However, the voltage of these systems is too low and unstable to be connected to the utility grid. Hence, high voltage converters should be used to increase the DC voltage of the fuel cell and PV into the DC voltage. The classic boost converter could be a suitable choice, owing to static voltage gain and simple structure [4]. A classic boost converter can be utilized to create high step-up voltage gain with high duty cycle. However, this converter has some disadvantage such as high switching losses, diode problem, and electromagnetic reverse-recovery interference (EMI) problem. In addition, the stresses of the switch and the diode of the classic boost converter are high. Hence, the high voltage rated switch should be used and the conduction and switching losses will be

**Research Paper**

increased. The maximum of the voltage gain of the classic boost cannot be more than five [5-9]. The quadratic boost converter is high voltage gain converter, which has only one main switch. The voltage gain of the converter is a quadratic function of a classic boost converter. The switch stress of the converter is equal to the output voltage. Hence, switch with high current can be selected [10-11]. Converters with the coupled inductor are good choices for achieving high voltage by adjusting the coupled inductor turns ratio. However, the coupled inductor leakage inductance makes high voltage stress of the switch and conduction loss. The switchedcapacitor technique can be used for earning high voltage. However, in these converters, many switches are utilized, which cause high losses. Some advantages of these converters are the low input ripple, high voltage gain, and low voltage stress of the switch [12-13]. In Ref. [14], a high voltage gain transformerless converter based on the switched inductor and capacitor and active network is proposed. This converter has two switches, which cause high conduction losses. The converter provides high voltage gain with low voltage stress. In Ref. [15], a transformerless converter with very high step-down voltage gain is proposed. In this converter, five power switches are utilized, which cause high switching and conduction losses. The voltage gain of the converter is three times lower compared to the voltage gain of the classic buck converter. In Ref. [16], a transformerless converter based on diode-capacitor cell is proposed. The converter has some advantages such as high voltage gain, low diodes and switches

Received: 14 Feb. 2019

Revised: 20 May 2019

Accepted: 25 Jul. 2019

<sup>\*</sup>Corresponding author: M. R. Banaei

E-mail: m.banaei@azaruniv.ac.ir (M. R. Banaei)

Digital object identifier: 10.22098/joape.2019.5363.1403

<sup>© 2020</sup> University of Mohaghegh Ardabili. All rights reserved.

stresses, low ripple, and high efficiency. In Ref. [17], high step-up transformerless converters are proposed. In these converters one main switch is used. In Ref. [18], a transformerless buck-boost converter is proposed. This converter has three main switches. In this converter, the voltage stress of the switch is equal to the output voltage. The converter conduction and switching losses are high. In Ref. [19], a buck-boost converter combining KY and the classic buck converter is proposed. In this converter two switches are used. Hence, the conduction and switching losses will be high. In Ref. [20], a transformerless buck-boost converter with high voltage gain is proposed. The voltage gain of the converter is squared times of the classic buck-boost converter. The stress of the switch and the diode is high. Hence, the losses of the converter will be high. In Ref. [21], a multi phase transformerless dc-dc converter with high voltage gain is proposed. The voltage stress of the converter is low. Hence, the losses can be reduced. In Ref. [22], a high step-down transformerless converter is suggested. In this converter, four switches are used. The voltage stress of the elements of the converter is high. Hence, the efficiency will be low. In Ref. [23], a DC-DC converter based on ZETA and Buck-Boost converters is presented. This converter has two-output. In the converter, one switch is used and converter has low number of components. In Ref. [24], a bidirectional dcdc converter based on ZETA converter is proposed. This converter has high conversion ratio and the leakageinductor energy can be recycled; therefore, the switch stress will be low. In Ref. [25], transformerless high step-up dc-dc converters are proposed. In Ref. [26], a high voltage gain converter is presented. In this converter, the switched inductor and three level converters are used. The converter has two switches; hence the conduction losses of the converter will be high. In Ref. [27], a high step-up converter is proposed. In this converter, active clamp circuit is used; therefore the voltage stress of the switch can be reduced. In Ref. [28] a high step-up transformerless converter is proposed. In this converter, two switches are used and the switched-inductor and switched-capacitor are utilized. In the converter, the output current is continuous. In Ref. [29] a buck-boost converter is suggested. The advantages of the converter are high voltage gain and positive output voltage. The converter has two switches and the voltage stresses of the switches are high and therefore, the losses of the converter will be high. In Ref. [30] a transformerless high step-up DC-DC converter based on the Cockcroft-Walton Voltage Multiplier is proposed. This converter employs two main switches and the diodes and switches stresses are high. In Ref. [31] a high step-up interleaved converter is presented. In this converter, the interleaved boost converter and the voltage-double module are used and the converter has two main switches and the stresses of the diodes of the converter are high. In Ref. [32] a high step-up converter with the coupled inductor is proposed. This converter has one main switch and the stress across the main switch is reduced. However, the voltage stresses of the three diodes of the converter are high. In this converter, the leakage inductance energy can be recycled. In Ref. [33] a transformerless buckboost converter is suggested. In this converter, one main switch is used. The switch voltage stress of the converter is high and therefore, the converter switch loss will be high. In referneces [34-37] high voltage gain transformerless converters are proposed. In this paper, a novel transformerless buck boost converter based on ZETA converter is proposed. The converter voltage gain is higher than the classic buck-boost converter, ZETA, CUK, and SEPIC converters. The proposed converter topology is very simple; hence, the converter control is simple. This converter has one main switch. The main switch and diodes stresses are less than the output voltage, hence the switch loss will be low and the converter efficiency can be improved. The buck-boost converters are used in some applications like LED drivers, fuel-cell, and car electronic devices. The modes analysis is explained and to confirm the operation of the converter, experimental results are given.

# 2. OPERATING PRINCIPLE OF THE PROPOSED CONVERTER

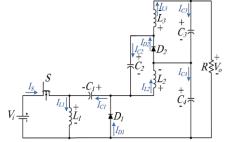

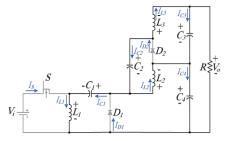

Fig. 1 shows the circuit topology of the presented converter. The converter consists one main switch S, two diodes  $D_1$  and  $D_2$ , three inductors  $L_1$ ,  $L_2$  and  $L_3$ , four capacitors  $C_1$ ,  $C_2$ ,  $C_3$  and  $C_4$  and load R.

To simplify the analysis of the new buck-boost converter, the following conditions were considered:

1) All capacitors are large enough hence; the voltages of the capacitors can be seen as constant.

2) Semiconductor elements such as diodes and switch are ideal.

The proposed converter can be used in the continuous conduction mode (CCM) and the discontinuous conduction mode (DCM). The continuous conduction mode has two operating modes. The analysis of the converter at (CCM) is presented in detail as follows:

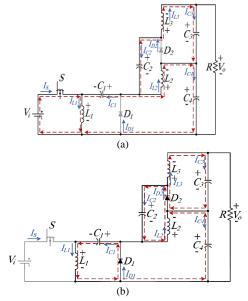

1) State 1  $[t_0,t_1]$ : During this time interval, the switch S is turned ON and the diodes  $D_1$  and  $D_2$  are

turned OFF. The current-flow path is shown in Fig. 2(a). The inductors  $L_1$ ,  $L_2$  and  $L_3$  are magnetized. The capacitor  $C_1$  and  $C_2$  are discharged and the capacitor  $C_4$  is charged. Thus, the corresponding equations can be achieved as follows:

$$V_{L1} = V_i \tag{1}$$

$$V_{L2} = V_{C1} + V_i - V_{C4} \tag{2}$$

$$V_{L3} = V_i + V_{C1} + V_{C2} - V_{C3} - V_{C4}$$

(3)

2) State 2  $[t_1, t_2]$ : The current-flow path is shown in Fig. 2(b). During this time interval, switch S is turned OFF. Diodes  $D_1$  and  $D_2$  are turned ON. The inductors  $L_1$ ,  $L_2$  and  $L_3$  are demagnetized. The capacitor  $C_1$  is charged by the inductor  $L_1$  and the capacitor  $C_2$  is charged by the inductor  $L_2$ . The capacitor  $C_4$  is discharged. The voltages of inductors are obtained as follows:

$$V_{L1} = -V_{C1}$$

(4)

$$V_{L2} = -V_{C2} = -V_{C4} \tag{5}$$

$$V_{L3} = -V_{C3}$$

(6)

# 3. STEADY STATE ANALYSIS OF THE PROPOSED CONVERTER

#### 3.1. Voltage gain

By applying volt-sec balance principle on  $L_1$ ,  $L_2$  and  $L_3$  and using (1)-(6), we have:

$$\frac{1}{T_{s}} \left( \int_{0}^{DT_{s}} (V_{i}) dt + \int_{DT_{s}}^{T_{s}} (-V_{C1}) dt \right) = 0$$

(7)

$$\frac{1}{T_{s}} \left( \int_{0}^{DT_{s}} (V_{C1} + V_{i} - V_{C4}) dt + \int_{DT_{s}}^{T_{s}} (-V_{C4}) dt \right) = 0$$

(8)

$$\frac{1}{T_{s}} \left( \int_{0}^{DT_{s}} (V_{i} + V_{C1} + V_{C2} - V_{C3} - V_{C4}) dt + \int_{DT_{s}}^{T_{s}} (-V_{C3}) dt \right) = 0$$

(9)

By using (5), (7), (8) and (9), the voltage of the capacitors  $C_1$ ,  $C_2$  and  $C_3$  ( $V_{C1}$ ,  $V_{C2}$ ,  $V_{C3}$  and  $V_{C4}$ ) can be achieved as follows:

$$V_{c1} = V_{c2} = V_{c3} = V_{c4} = \frac{D}{1 - D} V_i$$

(10)

By using (10), the voltage transfer gain  $(M_{CCM})$  can be found as follows:

$$M_{CCM} = \frac{V_o}{V_i} = \frac{2D}{1-D} \tag{11}$$

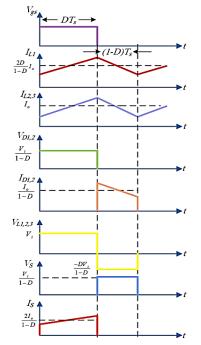

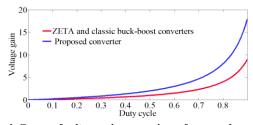

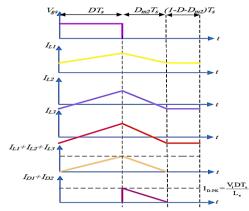

According to (11), it is apparent that the voltage gain of the proposed converter is twice as large as the ZETA converter. Therefore, the voltage gain of the converter is higher than that of ZETA converter. Fig. 3. shows some key waveforms of the proposed converter in (CCM).

Fig. 1. Circuit topology of the proposed converter

Fig. 2. Operation modes of the proposed converter (a) First mode, (b) Second mode

Fig. 3. Some waveforms of the proposed converter

Fig. 4. Curves of voltage gain comparison of proposed converter and other converters at CCM operation

The voltage gain curves for the proposed converter, ZETA and classic buck-boost converter are shown in Fig. 4. It is seen that the voltage transfer gain of the converter is higher than that of the other converters.

#### **3.2.** Calculation of the currents

The capacitor  $C_3$  performs as a low-pass filter, therefore the average current of the capacitors  $C_1$ ,  $C_2$ and  $C_4$  during state 1 ( $I_{C1,st1}$ ,  $I_{C2,st1}$  and  $I_{C4,st1}$ ) can be obtained as follows:

$$I_{C1,st1} = I_{C2,st1} - I_{L2}$$

(12)

$$I_{C2,\text{st1}} = -I_{L3} = -\frac{(2D)V_i}{(1-D)R}$$

(13)

$$I_{C4,st1} = I_{L2}$$

(14)

The average current of the capacitor  $C_4$  during state 2  $(I_{C4,st2})$  can be obtained as follows:

$$I_{C4,st2} = I_{L2} - I_{C2,st2}$$

(15)

Where,  $I_{C2,st2}$  is the average current of the capacitor  $C_2$  during state 2. By applying ampere-second balance principle on the capacitor  $C_4$  to yield:

$$\frac{1}{T_s} \left( \int_{0}^{DT_s} I_{C4,st1} dt + \int_{DT_s}^{T_s} I_{C4,st2} dt \right) = 0$$

(16)

By substituting (14) and (15) into (16), the average current of the capacitors  $C_1$ ,  $C_2$  and  $C_4$  during state 1 and the inductors  $L_1$ ,  $L_2$  and  $L_3$  ( $I_{C1,st1}$ ,  $I_{C2,st1}$ ,  $I_{C4,st1}$ ,  $I_{L1}$ ,  $I_{L2}$  and  $I_{L3}$ ) can be expressed as follows:

$$I_{C1,st1} = -\frac{(4D)V_i}{(1-D)R}$$

(17)

$$I_{C2,\text{st1}} = -I_{L3} = -\frac{(2D)V_i}{(1-D)R}$$

(18)

$$I_{C4,\text{st1}} = I_{L2} = \frac{(2D)V_i}{(1-D)R}$$

(19)

$$I_{L1} = I_{C1,st2} = \frac{(4D^2)W_i}{(1-D)^2R}$$

(20)

Table 1. The component normalized voltage and rms current stresses

| Circuit parameter          | Normalized voltage                 | Normalized rms current                            |  |

|----------------------------|------------------------------------|---------------------------------------------------|--|

| Switch S                   | $\frac{M_{_{CCM}}+2}{2M_{_{CCM}}}$ | $\frac{\sqrt{M_{CCM} + 2}}{\sqrt{M_{CCM}}}$       |  |

| Capacitor C <sub>1</sub>   | $\frac{1}{2}$                      | $\frac{\sqrt{2}}{\sqrt{M_{CCM}}}$                 |  |

| Capacitors $C_2$ and $C_4$ | $\frac{1}{2}$                      | $\frac{1}{\sqrt{2M_{CCM}}}$                       |  |

| Capacitor C <sub>3</sub>   | $\frac{1}{2}$                      | $\frac{R}{\sqrt{12}M_{CCM}(M_{CCM}+2)L_{s}f_{s}}$ |  |

| Diodes $D_1$ and $D_2$     | $\frac{M_{CCM} + 2}{2M_{CCM}}$     | $\frac{\sqrt{M_{CCM}+2}}{M_{CCM}\sqrt{2}}$        |  |

| Inductor $L_1$             | -                                  | 1                                                 |  |

| Inductors $L_2$ and $L_3$  | -                                  | $\frac{1}{M_{CCM}}$                               |  |

The current stress of the diodes  $D_1$  and  $D_2$  and the main switch  $S(I_{D1}, I_{D2} \text{ and } I_s)$  can be calculated as follows:

$$I_{D1} = I_{D2} = \frac{(2D)V_i}{(1-D)^2 R}$$

(21)

$$I_{s} = \frac{(4D)W_{i}}{(1-D)^{2}R}$$

(22)

The component normalized rms current and voltage stresses for the presented converter in CCM are shown in Table 1.

#### 3.3. Discontinuous conduction mode

There are three modes in Discontinuous conduction mode (DCM). The state 1 in (DCM) is the same as the state 1 in (CCM). In the state 2, the currents of the diodes will decrease. In the state 3, the current of the diodes decreases to zero. In this state, the diodes are turned off. The equivalent circuit is shown in Fig. 5. In this state, the inductors  $L_1$ ,  $L_2$  and  $L_3$  voltage will be zero.

According to Fig 2(b), the sum of the average currents of the diodes  $D_1$  and  $D_2$  can be earned as follows:

$$I_{D1} + I_{D2} = I_{L1} + I_{L2} + I_{L3}$$

(23)

The average of diodes  $D_1$  and  $D_2$  currents  $(I_{D1,av})$ and  $I_{D2,av}$  can be achieved as follows:

$$I_{D1,av} = I_{D2,av} = \frac{V_o}{R}$$

(24)

According to Fig. 6, the sum of the average of the diodes  $D_1$  and  $D_2$  over one switching period can be earned as follows:

$$I_{D1,av} + I_{D2,av} = \frac{1}{2} \times D_{m2} \times I_{D-PK}$$

(25)

Where,  $D_{m2}$  is duty cycle in state 2 under DCM and  $I_{D-PK}$  is sum of the inductors  $L_1$ ,  $L_2$  and  $L_3$  peak currents.

$$I_{D-pk} = I_{L1-pk} + I_{L2-pk} + I_{L3-pk} = \frac{V_i DT_s}{L_e}$$

(26)

Where,

$$\frac{1}{L_e} = \frac{1}{L_1} + \frac{1}{L_2} + \frac{1}{L_3}$$

(27)

By using volt-sec balance on inductors  $L_1$ ,  $L_2$  and  $L_3$  duty cycle in state 2 under DCM  $(D_{m2})$  can be obtained as follows:

$$D_{m2} = \frac{2DV_i}{V_o} \tag{28}$$

According to (23)-(28), the voltage gain of the converter in discontinuous conduction mode  $(M_{DCM})$  can be achieved as follows:

$$M_{DCM} = \frac{D}{\sqrt{\tau_L}}$$

(29)

Fig. 5. Equivalent circuits of the presented converter in third mode at DCM operation

Fig.6. Some illustrated waveforms of the proposed converter at DCM operation

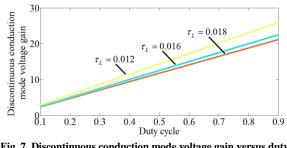

Fig. 7. Discontinuous conduction mode voltage gain versus duty cycle

Where, the normalized inductor time constant  $\tau_L$  is obtained as follows:

$$\tau_L = \frac{2L_e}{RT_s} \tag{30}$$

Fig. 7. shows the DCM voltage gain of the proposed converter versus duty cycle by different  $\tau_L$ .

## 3.4. Boundary condition mode

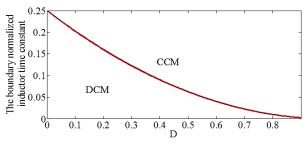

When the proposed converter is operated in boundary conduction mode (BCM) operation, the voltage gain in CCM is equal to DCM. Combing (11) and (29), the boundary normalized inductor time constant  $(\tau_b)$  is:

$$\tau_b = \frac{(1-D)^2}{4}$$

(31)

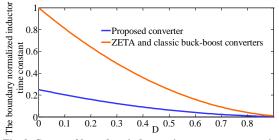

Fig. 8. shows the boundary normalized inductor time constant curve  $(\tau_b)$ . When  $\tau_L$  is larger than  $\tau_b$ , the presented buck-boost converter operates in CCM.

The boundary normalized inductor time constant curves for the proposed and the ZETA and classic buckboost converters are shown in Fig. 9.

Fig. 8. Boundary normalized inductor time constant versus duty cycle

Fig. 9. Curves of boundary inductor time constant comparison of proposed converter and other converters

#### 3.5. Efficiency analysis

For efficiency analysis of the presented buck-boost converter, parasitic resistances are defined as follows: switch on-state resistances is  $r_{DS}$ , forward resistances of the diodes  $D_1$  and  $D_2$  are  $R_{F1}$  and  $R_{F2}$ respectively,  $V_{F1}$  and  $V_{F2}$  are the threshold voltages of the diodes  $D_1$  and  $D_2$  respectively, inductors  $L_1$ ,  $L_2$  and  $L_3$  equivalent series resistances (ESR) are  $R_{L1}$ ,  $R_{L2}$  and  $R_{L3}$  respectively, the capacitors  $C_1$ ,  $C_2$ ,  $C_3$  and  $C_4$  ESR are  $r_{C1}$ ,  $r_{C2}$ ,  $r_{C3}$  and  $r_{C4}$ respectively and the voltage ripple of the capacitors and the inductors is ignored.

The condition loss of the switch  $S(P_{nDS})$  can be obtained as follows:

$$P_{rDS} = r_{DS} I_{S,ms}^{2} = r_{DS} \frac{4D}{(1-D)^{2}} I_{o}^{2}$$

(32)

The proposed converter switching loss  $(P_{Sw})$  can be achieved as follows:

$$P_{Sw} = f_{s}C_{S}V_{S}^{2} = f_{s}C_{S}\left(\frac{V_{i}}{1-D}\right)^{2}$$

(33)

The total losses of the switch  $S(P_{Switch})$  can be achieved as follows:

$$P_{Switch} = P_{rDS} + \frac{P_{Sw}}{2}$$

(34)

The losses of the diodes  $D_1$  and  $D_2(P_{D1,2})$  can be obtained as follows:

$$P_{D1,2} == R_{F1,2} \frac{1}{1-D} I_o^2 + V_{F1,2} I_o$$

(35)

The losses of capacitors  $C_1$ ,  $C_2$ ,  $C_3$  and  $C_4$  $\left(P_{C_{1,2,3,4}}\right)$  can be derived as:

$$P_{C1,2,3,4} = r_{C1} \frac{4DP_o}{(1-D)R} + r_{C2,4} \frac{DP_o}{(1-D)R} + r_{C3} \frac{(1-D)^2 RP_o}{48L_3^2 f_s^2}$$

(36)

The losses of inductors  $L_1$ ,  $L_2$  and  $L_3$   $(P_{L1,2,3})$  can be achieved as follows:

$$P_{L1,2,3} = R_{L1} \left(\frac{2D}{1-D}\right)^2 \frac{P_o}{R} + R_{L2,3} \frac{P_o}{R}$$

(37)

The total loss of the proposed converter  $(P_{Loss})$  can be expressed as follows:

$$P_{Loss} = P_{Switch} + \sum_{u=1}^{2} (P_{RF})_{Du} + \sum_{u=1}^{2} (P_{VF})_{Du} + \sum_{u=1}^{4} P_{RCu} + P_{rL1} + P_{rL2} + P_{rL3}$$

(38)

The efficiency of the proposed converter  $(\eta)$  can be

achieved as follows:

$$\eta = \frac{P_o}{P_o + P_{Loss}} = \frac{1}{1 + \frac{P_{Loss}}{P_o}}$$

(39)

According to above equations, the proposed converter efficiency can be obtained as follows:

$$\eta = \frac{1}{1 + \frac{A_1}{R(1-D)^2} + r_{C3}\frac{(1-D)^2R}{48Lf_s^2} + \frac{f_sC_sV_i^2}{2(1-D)^2RI_o^2}}$$

(40)

,

$$A_{1} = 4Dr_{DS} + (1-D)(R_{F1} + R_{F2}) + \frac{(1-D)}{I_{o}}(V_{F1} + V_{F2}) + 4D(1-D)r_{c1} + D(1-D)(r_{c2} + r_{c4}) + 4D^{2}R_{L1} + (1-D)^{2}(R_{L2} + R_{L3})$$

(41)

$(1 D)^2$

#### 3.6. Voltage stress

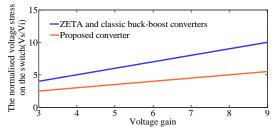

The voltage stress of the converter is an important parameter in the circuits. The voltage stress of the diodes and switch can be achieved as follows:

$$V_s = \frac{V_i}{1 - D} \tag{42}$$

$$V_{D1} = V_{D2} = \frac{V_i}{1 - D}$$

(43)

From Eq. (42) and Eq. (43), the voltage stresses of the diodes and switch are smaller than the output voltage. The comparison of the normalized voltage stress of the switch for the proposed converter and ZETA and classic buck-boost converters is shown in Fig. 10. The normalized voltage stress of the ZETA converter is higher than the presented converter therefore; the switch with low conduction loss can be selected.

Table 2 shows the comparison among the voltage and current stresses, efficiency, voltage gain and the number of elements of the converters. According to Table 2, the voltage gain of the proposed converter is higher than other converters comparing to the number of elements. The normalized voltage stress of the proposed converter is less than other converters and the structure of the converter is simple. The switch number of the proposed converter is less than that in the other converters.

As shown in Table 2, the proposed converter has much wider operating range than other converters and in this converter, only one power switch is used, but the costs of the extra switches of the converter in [18] and converter in [19] are high and control of the switches of the converters is complex. The total device of the other converters is higher comparing to their gains and voltage stresses. Based on the low voltage stress of the proposed converter, the efficiency of the proposed converter is higher comparing to its gain.

Fig. 10. Normalized switch voltage stress of the proposed converter versus voltage gain

Table 2. Comparison between proposed converter and other structures

|                                         | Proposed converter                      | Converter in [18]               |                                     | ZETA<br>converter       | KY<br>converter<br>in [19] |  |  |

|-----------------------------------------|-----------------------------------------|---------------------------------|-------------------------------------|-------------------------|----------------------------|--|--|

| Quantities of switches                  | 1                                       |                                 | 3                                   | 1                       | 2                          |  |  |

| Quantities<br>of diodes                 | 2                                       |                                 | 3                                   | 1                       | 1                          |  |  |

| Quantities<br>of<br>capacitors          | 4                                       |                                 | 1                                   | 2                       | 3                          |  |  |

| Quantities of inductors                 | 3                                       |                                 | 2                                   | 2                       | 2                          |  |  |

| Total device<br>count                   | 10                                      | 10                              |                                     | 6                       | 8                          |  |  |

| Voltage<br>stress of the<br>switch      | $\frac{\underline{V_o + 2} V_i}{2} V_i$ | 1                               | $\frac{V_o}{V_i}$ $\frac{V_o}{V_i}$ | $\frac{V_o + V_i}{V_i}$ | $rac{V_o}{V_i}$           |  |  |

| Voltage<br>gain                         | $\frac{2D}{1-D}$                        | $\frac{2D}{1-D}$                |                                     | $\frac{D}{1-D}$         | 2D                         |  |  |

| V <sub>Diode(Max)</sub> /V <sub>o</sub> | $\frac{1}{2D}$                          | 1                               |                                     | $\frac{1}{D}$           | $\frac{1}{2}$              |  |  |

| Average<br>current of<br>the diode      | I <sub>o</sub>                          | $I_o(1-2D)  \frac{I_o}{2}(1-D)$ |                                     | I                       | I <sub>o</sub>             |  |  |

| Maximum<br>efficiency                   | 97.2 %                                  | 90.2 %                          |                                     | 92.8 %                  | 94.8 %                     |  |  |

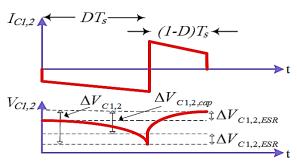

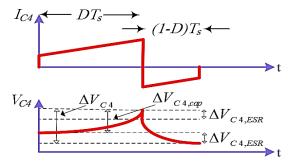

# **3.7.** Calculation of the voltage ripple of the capacitors

According to Fig. 11, the capacitor  $C_1$  voltage ripple called  $\Delta V_{C1}$ ,  $\Delta V_{C1,ESR}$  is created from the voltage ripple composed from the current of the equivalent series resistance of the capacitor  $C_1$  and the voltage ripple created from the charging and discharging of the capacitor  $C_1$  is denoted by  $\Delta V_{C1,cap}$ . Figs. 11-12. show the voltage and current of the capacitors  $C_2$  and  $C_4$ . Therefore, the voltage ripple of the capacitor  $C_1$  can be obtained as follows:

$$\Delta V_{C1} = \Delta V_{C1,ESR} + \Delta V_{C1,cap} \tag{44}$$

$\Delta V_{C1,ESR}$  can be achieved as follows:

$$\Delta V_{C1,ESR} = ESR_{C1}\Delta I_{C1} \simeq ESR_{C1}(I_{C1,on} - I_{C1,off}) = \frac{ESR_{C1}(4D)V_i}{(1-D)^2R}$$

(45)

Fig. 11. The current and voltage of the capacitors C1 and C2

Fig. 12. The current and voltage of the capacitor C<sub>4</sub>

Where,

$$ESR_{C1} = \frac{\tan \delta_{C1}}{2\pi f_s} \tag{46}$$

Where,  $\tan \delta_{c_1}$  is the dissipation factor of capacitor  $C_1$ .  $\Delta V_{C_{1,cap}}$  can be obtained as follows:

$$\Delta V_{C1,cap} = \frac{I_{C1,on} DT_s}{C_1} = \frac{2DT_s V_o}{RC_1}$$

(47)

Similarly, the voltage ripple of the capacitors  $C_2$  and  $C_4$  ( $\Delta V_{C2,4}$ ) can be expressed as follows:

$$\Delta V_{C2,4} = \Delta V_{C2,4,ESR} + \Delta V_{C2,4,cop} = \frac{ESR_{C2,4}(2D)V_i}{(1-D)^2R} + \frac{DT_sV_o}{RC_{2,4}}$$

(48)

#### 3.8. Capacitors and inductors design

The theoretical value of the inductors  $L_1$ ,  $L_2$  and  $L_3$  to work in CCM can be derived as follows:

$$L_{1} \ge \frac{V_{o}(1-D)^{2}}{8DI_{o}f_{s}} = \frac{92 \times (1-0.65)^{2}}{8 \times 0.65 \times 2.2 \times 43 \times 10^{3}} = 22 \mu H \quad (49)$$

$$L_{2,3} \ge \frac{V_o(1-D)}{4I_o f_s} = \frac{92 \times (1-0.65)}{4 \times 2.2 \times 43000} = 85 \mu H$$

(50)

The theoretical value of the capacitors  $C_1$ ,  $C_2$ ,  $C_3$ and  $C_4$  can be achieved as follows:

$$C_{1} \geq \frac{2DT_{s}V_{o}}{R\Delta V_{c1}} = \frac{2DV_{o}}{R\times 0.01 \times V_{o} \times f_{s}} = 2\times 0.65 \times 92$$

(51)

$$\frac{2 \times 0.65 \times 92}{42 \times 0.01 \times 92 \times 43000} = 71.9 \mu F$$

$$C_{2,4} \ge \frac{DT_s V_o}{R \Delta V_{c2,4}} = \frac{DV_o}{R \times 0.01 \times V_o \times f_s} =$$

$$0.65 \times 92$$

(52)

$$\frac{0.05 \times 92}{42 \times 0.01 \times 92 \times 43000} = 35.9 \mu F$$

$$C_{3} \ge \frac{V_{o}(1-D)}{16L_{3}f_{s}^{2}\Delta V_{C3}} = \frac{92 \times (1-0.65)}{16 \times 315 \times 10^{-6} \times (43 \times 10^{3})^{2} \times 1} = 3.45 \mu F \quad (53)$$

# 3.9. Small signal modeling

According to Fig. 2(a), the equations for the state 1 can be achieved as follows:

$$L_1 \frac{di_{L1}}{dt} = V_i \tag{54}$$

$$L_2 \frac{di_{L2}}{dt} = V_{C1} - V_{C4} + V_i \tag{55}$$

$$L_{3}\frac{di_{L3}}{dt} = V_{C1} + V_{C2} + V_{i} - V_{C3} - V_{C4}$$

(56)

$$C_1 \frac{dV_{C1}}{dt} = -i_{L2} - i_{L3} \tag{57}$$

$$C_2 \frac{dV_{C2}}{dt} = -i_{L3}$$

(58)

$$C_{3} \frac{dV_{C3}}{dt} = i_{L3} - \frac{V_{C3} + V_{C4}}{R}$$

(59)

$$C_4 \frac{dV_{C4}}{dt} = i_{L2} + i_{L3} - \frac{V_{C3} + V_{C4}}{R}$$

(60)

According to Fig 2(b), the equations for the state 2 can be expressed as follows:

$$L_1 \frac{di_{L1}}{dt} = -V_{C1} \tag{61}$$

$$L_2 \frac{di_{L2}}{dt} = -V_{C2}$$

(62)

$$L_3 \frac{di_{L3}}{dt} = -V_{C3}$$

(63)

$$C_1 \frac{dV_{C1}}{dt} = i_{L1}$$

(64)

$$C_{2}\frac{dV_{C2}}{dt} = -\frac{1}{1-d}\frac{V_{C3} + V_{C4}}{R} + \frac{1}{1-d}i_{L2} + \frac{d}{1-d}i_{L3} \quad (65)$$

$$C_{3} \frac{dV_{C3}}{dt} = i_{L3} - \frac{V_{C3} + V_{C4}}{R}$$

(66)

$$C_4 \frac{dV_{C4}}{dt} = i_{L2} - \frac{d}{1-d} i_{L3} - \frac{V_{C3} + V_{C4}}{R}$$

(67)

According to the average method and using equations (54)-(67), the average model for the proposed converter can be achieved as follows:

$$L_{1} \frac{d \left\langle i_{L1} \right\rangle}{dt} = d \left\langle V_{i} \right\rangle - (1 - d) \left\langle V_{C1} \right\rangle$$

(68)

$$L_{2} \frac{d\langle i_{L2} \rangle}{dt} = d \langle V_{C1} \rangle - d \langle V_{C4} \rangle + d \langle V_{i} \rangle - (1-d) \langle V_{C2} \rangle$$

(69)

$$L_{3} \frac{d\langle i_{L3} \rangle}{dt} = d\langle V_{C1} \rangle + d\langle V_{C2} \rangle + d\langle V_{i} \rangle - \langle V_{C3} \rangle - d\langle V_{C4} \rangle$$

(70)

$$C_{1} \frac{d \langle V_{C1} \rangle}{dt} = -d \langle i_{L2} \rangle - d \langle i_{L3} \rangle + (1-d) \langle i_{L1} \rangle$$

(71)

$$C_{2} \frac{d \left\langle V_{C2} \right\rangle}{dt} = \left\langle i_{L2} \right\rangle - \frac{\left\langle V_{C3} \right\rangle + \left\langle V_{C4} \right\rangle}{R} \tag{72}$$

$$C_{3} \frac{d \langle V_{C3} \rangle}{dt} = \langle i_{L3} \rangle - \frac{\langle V_{C3} \rangle + \langle V_{C4} \rangle}{R}$$

(73)

$$C_{4} \frac{d \left\langle V_{C4} \right\rangle}{dt} = \left\langle i_{L2} \right\rangle - \frac{\left\langle V_{C3} \right\rangle + \left\langle V_{C4} \right\rangle}{R} \tag{74}$$

where  $\langle i_{L1} \rangle$ ,  $\langle i_{L2} \rangle$ ,  $\langle i_{L3} \rangle$ ,  $\langle V_{C1} \rangle$ ,  $\langle V_{C2} \rangle$ ,  $\langle V_{C3} \rangle$ ,  $\langle V_{C4} \rangle$  and  $\langle V_i \rangle$  are the average values of  $i_{L1}$ ,  $i_{L2}$ ,  $i_{L3}$ ,  $V_{C1}$ ,  $V_{C2}$ ,  $V_{C3}$ ,  $V_{C4}$  and  $V_i$  respectively, and d is the duty cycle.

For obtaining the small-signal model, small AC values of the mentioned elements are defined as:

$$\hat{i}_{L1}$$

,  $\hat{i}_{L2}$ ,  $\hat{i}_{L3}$ ,  $\hat{V}_{C1}$ ,  $\hat{V}_{C2}$ ,  $\hat{V}_{C3}$ ,  $\hat{V}_{C4}$ ,  $\hat{V}_i$  and  $\hat{d}$ . In addition, the relationship among DC values, AC values and average values can be earned as follows:

$$\langle V_i \rangle = V_i + V_i \quad \text{and} \quad V_i \ll V_i$$

(75)

$$\langle d \rangle = d + d$$

and  $d \ll d$  (76)

$$\langle i_{L1} \rangle = i_{L1} + i_{L1}$$

and  $i_{L1} \ll i_{L1}$  (77)

$$\langle i_{L2} \rangle = i_{L2} + i_{L2}$$

and  $i_{L2} \ll i_{L2}$  (78)

$$\langle i_{L3} \rangle = i_{L3} + i_{L3}$$

and  $i_{L3} \ll i_{L3}$  (79)

$$\langle V_{c1} \rangle = V_{c1} + \hat{V_{c1}} \quad \text{and} \quad \hat{V_{c1}} \ll V_{c1} \tag{80}$$

$$\left\langle V_{C2} \right\rangle = V_{C2} + V_{C2} \text{ and } V_{C2} \ll V_{C2}$$

(81)

$$\langle V_{C3} \rangle = V_{C3} + \hat{V}_{C3} \text{ and } \hat{V}_{C3} \ll V_{C3}$$

$$(82)$$

$$\langle V_{C4} \rangle = V_{C4} + \hat{V_{C4}} \text{ and } \hat{V_{C4}} \ll V_{C4}$$

(83)

By substituting (75)-(83) into (68)-(74), extracting the DC and AC values and omitting the higher order small signal terms we have:

$$L_{1}\frac{d\hat{i}_{L1}}{dt} = d\hat{V}_{i} + \hat{d}(V_{C1} + V_{i}) - (1 - d)\hat{V}_{C1}$$

(84)

$$L_{2} \frac{d\hat{l}_{L2}}{dt} = d\hat{V}_{c1} - d\hat{V}_{c4} + \hat{d}(V_{c1} - V_{c4} + V_{i} + V_{c2}) + d\hat{V}_{i} - (1 - d)\hat{V}_{c2}$$

(85)

$$L_{3}\frac{d\hat{i}_{L3}}{dt} = d\hat{V}_{c1} + d\hat{V}_{c2} - \hat{V}_{c3} - d\hat{V}_{c4} +$$

$$\hat{d}\hat{V}_{c4} - \hat{V}_{c4} + \hat{V}_$$

$$d(V_{c1} - V_{c4} + V_i + V_{c2}) + dV_i$$

$$C_1 \frac{d\hat{V}_{c1}}{dt} = -d\hat{i}_{L2} + \hat{d}(-i_{L1} - i_{L2} - i_{L3}) - d\hat{i}_{L3} + (1 - d)\hat{i}_{L_1}$$

(87)

$$C_2 \frac{d\hat{V}_{C2}}{dt} = \hat{i}_{L2} - \frac{\hat{V}_{C3} + \hat{V}_{C4}}{R}$$

(88)

$$C_{3}\frac{d\hat{V}_{C3}}{dt} = \hat{i}_{L3} - \frac{\hat{V}_{C3} + \hat{V}_{C4}}{R}$$

(89)

$$C_4 \frac{d\hat{V}_{C4}}{dt} = \hat{i}_{L2} - \frac{\hat{V}_{C3} + \hat{V}_{C4}}{R}$$

(90)

From equations (84)-(90), the state-space form of the equations can be achieved as follows:

$$\begin{aligned} Kx &= Ax + Bu \end{aligned} \tag{91} \\ y &= Cx + Eu \end{aligned} \tag{92}$$

with

$$x = \begin{bmatrix} \hat{i}_{L1} & \hat{i}_{L2} & \hat{i}_{L3} & \hat{V}_{C1} & \hat{V}_{C2} & \hat{V}_{C3} & \hat{V}_{C4} \end{bmatrix}^T$$

(93)

$$u = \begin{bmatrix} \hat{d} & \hat{V_i} \end{bmatrix}^T$$

(94)

$$K = \begin{bmatrix} L_1 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & L_2 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & L_3 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & C_1 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & C_2 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & C_3 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & C_4 \end{bmatrix}$$

(95)

$$A = \begin{bmatrix} 0 & 0 & 0 & -(1-d) & 0 & 0 & 0 \\ 0 & 0 & 0 & d & -(1-d) & 0 & -d \\ 0 & 0 & 0 & d & d & -1 & -d \\ (1-d) & -d & -d & 0 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 & 0 & -\frac{1}{R} & -\frac{1}{R} \\ 0 & 0 & 1 & 0 & 0 & 0 & -\frac{1}{R} & -\frac{1}{R} \\ 0 & 1 & 0 & 0 & 0 & -\frac{1}{R} & -\frac{1}{R} \end{bmatrix}$$

(96)

$$B = \begin{bmatrix} V_i + V_{C1} & d \\ V_i - V_{C4} + V_{C1} + V_{C2} & d \\ V_{C1} + V_{C2} + V_i - V_{C4} & d \\ -i_{L1} - i_{L2} - i_{L3} & 0 \\ 0 & 0 \\ 0 & 0 \end{bmatrix}$$

(97)

The matrices for the output equation (y) can be obtained as follows:

$$V_{o} = \begin{bmatrix} 0 & 0 & 0 & 0 & 1 & 1 \end{bmatrix} \begin{bmatrix} \hat{i}_{L1} \\ \hat{i}_{L2} \\ \hat{i}_{L3} \\ \hat{V}_{C1} \\ \hat{V}_{C2} \\ \hat{V}_{C3} \\ \hat{V}_{C4} \end{bmatrix} + \begin{bmatrix} 0 & 0 \end{bmatrix} \begin{bmatrix} \hat{d} \\ \hat{V}_{i} \end{bmatrix}$$

(98)

#### 4. EXPERIMENTAL RESULTS

In order to verify the performance of the presented converter, experimental results are provided. A prototype of the proposed converter is built as shown in Fig. 13.

The proposed converter utilized components are as follows:

- 1) Input voltage : 25 V

- 2) Switching frequency: 43 kHz

- 3) switch: IRFP460A

- 4) switch on-state resistance: 0.03 ohm

- 5) diodes  $D_1$  and  $D_2$ : MUR860

- 6) diodes  $D_1$  and  $D_2$  forward resistances: 0.02 ohm

- 7) diodes  $D_1$  and  $D_2$  threshold voltages: 0.7 V

- 8) inductor  $L_1$ : 150  $\mu$ H

- 9) inductors  $L_2$  and  $L_3$ : 315  $\mu$ H

- 10) the equivalent series resistances (ESR) of inductor  $L_1$ :0.01 ohm

- 11) the equivalent series resistances (ESR) of inductors  $L_2$  and  $L_3$  :0.018 ohm

- 12) capacitors  $C_2$ ,  $C_3$  and  $C_4$ : 100  $\mu$ F

- 13) capacitor  $C_1$ : 470 µF

- 14) the equivalent series resistances (ESR)of capacitors  $C_2$ ,  $C_3$  and  $C_4$ : 0.012 ohm

- 15) the equivalent series resistances (ESR)of capacitor  $C_1$ : 0.023 ohm

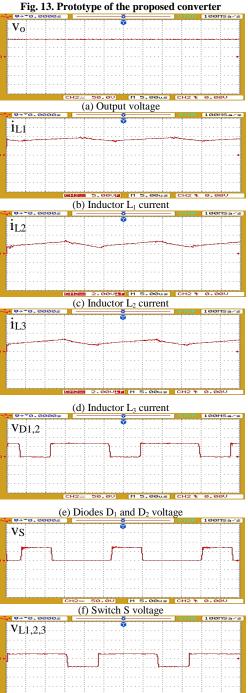

The output voltage is shown in Fig. 14(a). The output voltage is 92 V and the output power is 200 W. Figs. 14(b), 14(c) and 14(d) show the waveform of the inductors currents of  $L_1$ ,  $L_2$  and  $L_3$  respectively. According to Eqns. (18)-(20), the average of inductors currents of  $L_1$ ,  $L_2$  and  $L_3$  are 8.1, 2.2 and 2.2 A respectively. The diode  $D_2$  voltage waveform is similar to diode  $D_1$  voltage waveform. The voltage on the diodes  $D_1$  and  $D_2$  is given in Fig. 14(e). According to Eq. (43), the voltage on the switch

S is shown in Fig. 14(f). According to (42), the switch S voltage is 71 V. The voltage of inductors  $L_1$ ,  $L_2$  and  $L_3$  is shown in Fig. 14(g). The voltage of inductors  $L_1$ ,  $L_2$  and  $L_3$  during state 1 is 25 V and during state 2 is equal to -46 V. Fig. 14(h) shows the waveform of the diodes currents of  $D_1$  and  $D_2$ . According to (21), the average of diodes currents of  $D_1$  and  $D_2$  is 6.25 A. Fig. 14(i) shows the waveform of the switch S current. According to (22), the average of switch S current is 12.5 A.

The conventional ZETA converter used components are as follows:

- 1) input voltage : 25 V

- 2) switching frequency: 43 kHz

- 3) switch on-state resistance: 0.03 ohm

- 4) diode  $D_1$  forward resistance: 0.02 ohm

- 5) diode  $D_1$  threshold voltage: 0.7 V

- 6) inductor  $L_1$ : 150 µH

- 7) inductor  $L_2$ : 315  $\mu$ H

- 8) the equivalent series resistances (ESR) of inductor  $L_1$ :0.01 ohm

- 9) the equivalent series resistances (ESR) of inductor  $L_2$  :0.018 ohm

- 10) capacitor  $C_1$ : 100 µF

- 11) capacitor  $C_2$ : 470 µF

- 12) the equivalent series resistances (ESR)of capacitor  $C_1$ : 0.023 ohm

- 13) the equivalent series resistances (ESR)of capacitor  $C_2$  : 0.012 ohm

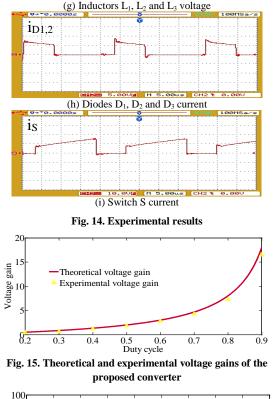

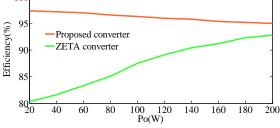

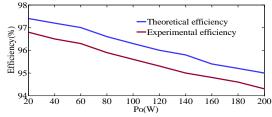

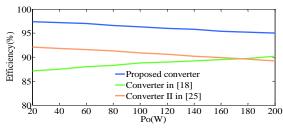

Fig. 15 shows the theoretical and experimental voltage transfer gains of the proposed converter. Fig. 16 shows the efficiency curves of converters with different output power. It is seen that the efficiency of proposed converter is higher than that of ZETA converter. Fig. 17. shows the curve of efficiency of the proposed converter versus output power. It is seen that the theoretical efficiency is higher than the experimental efficiency. Fig. 18 shows the efficiency curves of converters with different output power. It is seen that the theoretical efficiency is higher than the experimental efficiency. Fig. 18 shows the efficiency curves of converters with different output power. It is seen that the efficiency of proposed converter is higher than that of the converter in Ref. [18] and converter II in Ref. [25].

Fig. 16. Measured efficiency of the converters versus output power

Fig. 17. Measured efficiency of the presented converter versus output power

Fig. 18. Measured efficiency of the proposed converter and other converters versus output power

#### 5. CONCLUSIONS

In this paper, a novel transformerless buck boost

converter based on ZETA converter is presented. In this converter, only one main switch is used, which decreases the losses and improves efficiency. The active switch voltage stress is low and switch with low onstate resistance can be utilized. The voltage gain of the converter is higher than that of the classic boost, buckboost, ZETA, CUK and SEPIC converters. The presented converter structure is simple; hence, the converter control is simple. The buck-boost converters are used in some applications such as fuel-cell, car electronic devices, and LED drivers. Finally, the experimental results are given to verify the proposed converter.

#### REFERENCES

- B. Kjaer, K. Pedersen, and F. Blaabjerg, "A review of singlephase grid-connected inverters for photovoltaic modules", *IEEE Trans. Ind. Electron.*, vol. 41, no. 5, pp. 1292-1306, 2005.

- [2] D. Meneses, F. Blaabjery, O. Garcia, J. A. Cobos, "Review and comparison of step-up transformerless topologies for photovoltaic AC-module application", *IEEE Trans. Power Electron.*, vol. 28, no. 6, pp. 2649-2663, 2013.

- [3] H. S. Lee, H. J. Choe, S. H. Ham and B. Kang, "Highefficiency asymmetric forward-flyback converter for wide output power range", *IEEE Trans. Power Electron.*, vol. 32, no. 1, pp. 433-440, 2017.

- [4] N. Mohan, T. M. Undeland and W. P. Robbins, "Power Electronis: converters applications and design", New York: John Wiley & Sons, 1995.

- [5] S. K. Changchien, T. J. Liang, J. F. Chen and L. S. Yang, "Step-up DC-DC converter by coupled inductor and voltage-lift technique", *IET Power Electron.*, vol. 3, no. 3, pp. 369-378, 2010.

- [6] W. Li and X. He, "Review of nonisolated high-step-up DC/DC converters in photovoltaic grid-connected applications", *IEEE Trans. Ind. Electron.*, vol. 58, no. 4, pp. 1239-1250, 2011.

- [7] M. Nymand and M. A. Andersen, "High-efficiency isolated boost DC–DC converter for high-power lowvoltage fuel-cell applications", *IEEE Trans. Ind. Electron.*, vol. 589, no. 2, pp. 505-514, 2010.

- [8] F. L. Tofoli, D. C. Pereira, W. J. Paula and D. S. Junior, "Survey on non-isolated high-voltage step-up DC–DC topologies based on the boost converter", *IET Power Electron.*, vol. 8, no. 8, pp. 2044-2057, 2015.

- [9] X. Zhu, B. Zhang, Z. Li, H. Li and L. Ran, "Extended switched-boost DC-DC converters adopting switchedcapacitor/switched-inductor cells for high step-up conversion", *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 5, no. 3, pp. 1020-1030, 2017.

- [10] L. Barreto, E. Coelho, V. Farias, J. de Oliveira, L. de Freitas, and J. Vieira, "A quasi-resonant quadratic boost converter using a single resonant network", *IEEE Trans. Ind. Electron.*, vol. 52, no. 2, pp. 552-557, 2005.

- [11] B. R. Lin and H. H. Lu, "Single-phase three-level PWM rectifier", in Proc. IEEE APEC, pp. 63-68, 1999.

- [12] C. L. Wei and M. H. Shih, "Design of a switched capacitor DC-DC converter with a wide input voltage range", *IEEE Trans. Circuits Syst.*, vol. 60, no. 6, pp. 1648-1656, 2013.

- [13] K. C. Tseng and C. C. Huang, "High step-up highefficiency interleaved converter with voltage multiplier module for renewable energy system", *IEEE Trans. Ind. Electron.*, vol. 61, no. 3, pp. 1311-1319, 2013.

- [14] Y. Tang, T. Wang and D. Fu, "Multicell switchedinductor/switched-capacitor combined active-network converters", *IEEE Trans. Power Electron.*, vol. 30, no. 4, pp. 2063-2072, 2015.

- [15] O. Kirshenboim and M. M. Peretz, "High-efficiency nonisolated converter with very high step-down conversion ratio", *IEEE Trans. Power Electron.*, vol. 32, no. 5, pp. 3683-3690, 2017.

- [16] S. Hou, J. Chen, T. Sun and X. Bi, "Multi-input step-up converters based on the switched-diode-capacitor voltage accumulator", *IEEE Trans. Power Electron.*, vol. 31, no. 1, pp. 381-393, 2016.

- [17] G. Wu, X. Ruan and Z. Ye, "Nonisolated high step-up DC–DC converters adopting switched-capacitor cell", *IEEE Trans. Ind. Electron.*, vol. 62, no. 1, pp. 383-393, 2015.

- [18] H. K. Liao, T. J. Liang, L. S. Yang and J. F. Chen, "Noninverting buck-boost converter with interleaved technique for fuel-cell system", *IET Power Electron.*, vol. 5, no. 8, pp. 1379-1388, 2012.

- [19] K. Hwu and T. Peng, "A Novel buck-boost converter combining KY and buck converters", *IEEE Trans. Power Electron.*, vol. 27, no. 5, pp. 2236-2241, 2012.

- [20] S. Miao, F. Wang and X. Ma, "A new transformerless buck-boost converter with positive output voltage", *IEEE Trans. Ind. Electron.*, vol. 63, no. 5, pp. 2965-2975, 2016.

- [21] K. I. Hwu and W. Z. Jiang, "Analysis, design and derivation of a two-phase converter", *IET Power Electron.*, vol. 8, no. 10, pp. 1987-1995, 2015.

- [22] C. T. Pan, C. F. Chuang and C. C. Chu, "A novel transformerless interleaved high step-down conversion ratio DC–DC converter with low switch voltage stress", *IEEE Trans. Ind. Electron.*, vol. 61, no. 10, pp. 5290-5299, 2014.

- [23] A. Andrade, L. Schuch and M. Martins, "Very high voltage step-up Integrated Quadratic-Boost-Zeta converter", *in Proc. IEEE 24th Int. Symp. Ind. Electron.* (*ISIE*), pp. 422-427, 2015.

- [24] H. Y. Lee, T. J. Liang, J. F. Chen and K. H. Chen, "Design and implementation of a bidirectional SEPIC-Zeta DC-DC Converter", in Proc. IEEE Int. Symp. Circuits Syst. (ISCAS), pp. 101-104, 2014.

- [25] L. Yang, T. Liang and J. Chen, "Transformerless DC–DC converters with high step-up voltage gain", *IEEE Trans. Ind. Electron.*, vol. 56, no. 8, pp. 3144-3152, 2009.

- [26] E. Salari, M. R. Banaei and A. Ajami, "Analysis of switched inductor three-level DC/DC converter", J. Oper. Autom. Power Eng., vol. 6, no.1, pp. 126-134, 2018.

- [27] E. Babaei, M. Baruji, H. Mashinchi Maheri, and A. Abbasnezhad, "A developed structure of step-up DC/DC converter by using coupled inductor and active clamped circuit", *J. Oper. Autom. Power Eng.*, vol. 5, no.1, pp. 31-42, 2017.

- [28] M. A. Salvador, T. B. Lazzarin and R. F. Coelho, "High Step-Up DC–DC Converter with Active Switched-Inductor and Passive Switched-Capacitor Networks", *IEEE Trans. Ind. Electrons.*, vol. 65, no. 7, pp. 5644-5654, 2018.

- [29] J. Caro, J. Resendiz, J. Maldonado, A. Reyes and A. Gonzalez, "Quadratic buck-boost converter with positive output voltage and minimum ripple point design", *IET Power Electron.*, vol. 11, no. 7, pp. 1306-1313, 2018.

- [30] A. Rajaei, R. Khazan, M. Mahmoudian, M. Mardaneh and M. Gitizadeh, "A Dual Inductor High Step-Up DC/DC Converter Based on the Cockcroft-Walton Multiplier", *IEEE Trans. Power Electron.*, vol. 33, no. 11, pp. 9699-9709, 2018.

- [31] Y. Chen, Z. Lu and R. Liang, "Analysis and Design of a Novel High-Step-Up DC/DC Converter With Coupled Inductors", *IEEE Trans. Power Electron.*, vol. 33, no. 1, pp. 425-436, 2018.

- [32] J. Ai and M. Lin, "High step-up DC–DC converter with low power device voltage stress for a distributed generation system", *IET Power Electron.*, vol. 11, no. 12, pp. 1955-1963, 2018.

- [33] V. Pires, D. Foito, A. Cordeiro and J. Silva, "A single-switch DC/DC buck-boost converter with extended output voltage", 2018 7th Int. Conf. Renewable Energy Res. Appl. (ICRERA), pp. 791-796, Paris, France, 2018.

- [34] M. R. Banaei and H. A. F. Bonab, "A nonisolated transformerless high voltage gain buck boost dc-dc converter", *Modares J. Electr. Eng.*, vol. 15, no. 3, pp. 9-19, 2015.

- [35] M. R. Banaei and H. A. F. Bonab, "High Efficiency Transformerless Buck Boost DC-DC Converter", *Int. J. Circ. Theor. Appl.*, vol. 45, no. 8, pp. 1129-1150, 2017.

- [36] H. A. F. Bonab and M. R. Banaei, "A Novel High Step-Up DC-DC Converter Based on KY Converter", *JEEE J.*, vol. 10, no. 1, pp. 5-10, 2016.

- [37] M. R. Banaei, H. A. F. Bonab, "A novel structure for single-switch nonisolated transformerless buck–boost DC–DC converter", *IEEE Trans. Ind. Electron.*, vol. 64, no. 1, pp. 198-205, 2017.